數(shù)字集成電路版圖設(shè)計(jì)(二) 基于Cadence IC的簡(jiǎn)單反相器版圖設(shè)計(jì)實(shí)踐

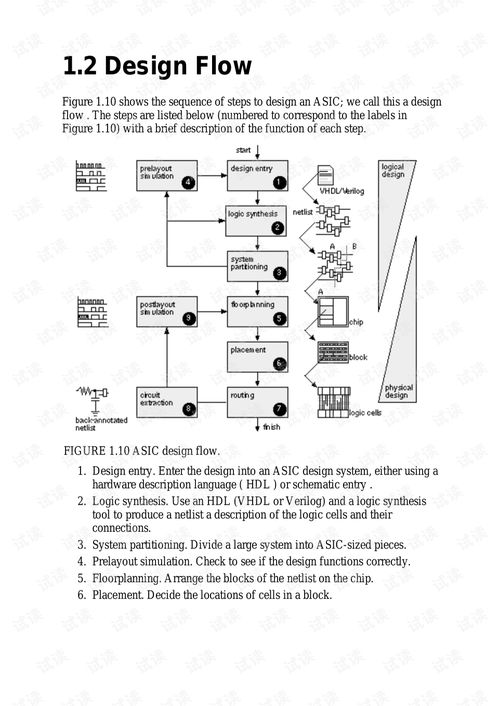

在數(shù)字集成電路設(shè)計(jì)流程中,版圖設(shè)計(jì)是將邏輯電路轉(zhuǎn)化為物理實(shí)現(xiàn)的關(guān)鍵一步。反相器作為數(shù)字電路中最基本、最核心的單元,其版圖設(shè)計(jì)是初學(xué)者掌握版圖設(shè)計(jì)理念與工具的絕佳起點(diǎn)。本文將介紹如何使用業(yè)界主流的Cadence IC設(shè)計(jì)工具,完成一個(gè)簡(jiǎn)單反相器的版圖設(shè)計(jì)。

一、設(shè)計(jì)準(zhǔn)備與目標(biāo)

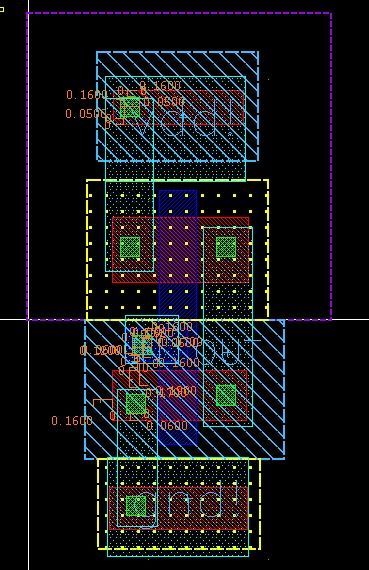

在開始設(shè)計(jì)前,需明確設(shè)計(jì)目標(biāo):采用特定工藝(例如某180nm CMOS工藝),設(shè)計(jì)一個(gè)驅(qū)動(dòng)能力適中的標(biāo)準(zhǔn)反相器。其原理圖通常由一個(gè)PMOS管和一個(gè)NMOS管組成,輸入端共用,輸出端連接兩管的漏極。我們需要在版圖設(shè)計(jì)中實(shí)現(xiàn)這一電氣連接,并滿足工藝設(shè)計(jì)規(guī)則(Design Rules),確保最終的可制造性和可靠性。

二、Cadence IC環(huán)境啟動(dòng)與單元?jiǎng)?chuàng)建

- 啟動(dòng)Cadence Virtuoso,并建立或載入相應(yīng)工藝的設(shè)計(jì)庫(kù)(Technology Library)。

- 在庫(kù)管理器中,創(chuàng)建一個(gè)新的版圖單元視圖(Layout Cell View),命名為“INV”。

三、版圖繪制核心步驟

- 繪制有源區(qū)(Active Area):在版圖編輯窗口,選擇“Active”或“Diffusion”層,分別繪制PMOS和NMOS晶體管所需的有源區(qū)矩形。兩者之間需保持足夠的間距以滿足設(shè)計(jì)規(guī)則。

- 繪制多晶硅柵極(Poly Gate):選擇“Poly”層,繪制一個(gè)橫跨PMOS和NMOS有源區(qū)的長(zhǎng)條形矩形,形成反相器的公共輸入端(柵極)。多晶硅與有源區(qū)相交的部分即定義了晶體管的溝道區(qū)域。

- 繪制選擇層(Select/Implant):分別繪制P型選擇層(P-Select)覆蓋PMOS有源區(qū),以及N型選擇層(N-Select)覆蓋NMOS有源區(qū),以定義阱內(nèi)摻雜類型,從而區(qū)分PMOS和NMOS。

- 繪制接觸孔與金屬連線:

- 電源與地:在PMOS有源區(qū)上端,通過(guò)“Contact”或“Via”層繪制接觸孔,并用第一層金屬(Metal1)連接到VDD電源線。在NMOS有源區(qū)下端,同樣繪制接觸孔并用Metal1連接到VSS(地)線。

- 輸入與輸出:在公共多晶硅柵極上打接觸孔,并用Metal1引出一段導(dǎo)線作為輸入端口(A)。在PMOS與NMOS有源區(qū)相鄰的區(qū)域(即兩管的漏極交匯處),繪制接觸孔,并用Metal1連接起來(lái),形成輸出端口(Y)。

- 添加N阱(N-Well):PMOS管需要制作在N阱中。使用“NWell”層繪制一個(gè)矩形,完全包圍PMOS的有源區(qū)及其周邊區(qū)域,并確保與NMOS區(qū)域有足夠間隔。

- 添加引腳標(biāo)識(shí)(Pin):使用“Pin”層或文本工具,為金屬連線上的輸入(A)、輸出(Y)、電源(VDD)和地(VSS)添加清晰的標(biāo)簽,這些標(biāo)簽將在后續(xù)的電路提取與驗(yàn)證中使用。

四、設(shè)計(jì)規(guī)則檢查(DRC)

完成圖形繪制后,必須運(yùn)行設(shè)計(jì)規(guī)則檢查。在Virtuoso中調(diào)用DRC工具,選擇對(duì)應(yīng)的工藝規(guī)則文件。DRC工具會(huì)自動(dòng)檢查版圖中所有幾何圖形的最小寬度、最小間距、包圍、延伸等規(guī)則是否違反。根據(jù)報(bào)告的錯(cuò)誤與警告,逐一修改版圖,直至通過(guò)所有檢查(DRC Clean)。這是保證芯片能夠被成功制造的基礎(chǔ)。

五、版圖與電路圖一致性檢查(LVS)

LVS驗(yàn)證是確保物理版圖與原始邏輯電路圖在電氣連接上完全一致的關(guān)鍵步驟。

- 首先需要有一個(gè)正確的反相器電路圖(Schematic)。

- 在LVS工具中,設(shè)置版圖網(wǎng)表提取和電路圖網(wǎng)表提取的路徑。

- 運(yùn)行LVS,工具會(huì)從版圖中提取出器件(兩個(gè)MOS管)及其連接關(guān)系,并與電路圖進(jìn)行比對(duì)。

- 如果LVS通過(guò)(Netlists match),表明版圖連接正確。如果失敗,需根據(jù)報(bào)告仔細(xì)排查是器件類型、尺寸不符,還是連接關(guān)系(如短路、開路)有誤。

六、后仿真考慮與完成

通過(guò)DRC和LVS后,一個(gè)可制造且連接正確的反相器版圖即告完成。為了評(píng)估其性能,可以進(jìn)行寄生參數(shù)提取(如使用RCX工具),生成包含寄生電阻電容的網(wǎng)表,并返回到仿真環(huán)境(如Spectre)中進(jìn)行后仿真,觀察其瞬態(tài)響應(yīng)、延遲和功耗,并與前仿真結(jié)果對(duì)比,以評(píng)估版圖引入的寄生效應(yīng)影響。

通過(guò)這個(gè)簡(jiǎn)單的反相器版圖設(shè)計(jì)實(shí)踐,我們走完了從圖形繪制、設(shè)計(jì)規(guī)則遵守到電氣驗(yàn)證的完整版圖設(shè)計(jì)子流程。它深刻體現(xiàn)了版圖設(shè)計(jì)不僅是“畫畫”,更是對(duì)工藝規(guī)則的嚴(yán)格遵守、對(duì)電氣連接的精確實(shí)現(xiàn)以及對(duì)電路性能的物理保障。掌握這一基礎(chǔ)單元的設(shè)計(jì),為進(jìn)一步學(xué)習(xí)更復(fù)雜的組合邏輯(如與非門、或非門)和時(shí)序邏輯(如觸發(fā)器)的版圖設(shè)計(jì)打下了堅(jiān)實(shí)的基礎(chǔ)。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://m.gzclyk.cn/product/63.html

更新時(shí)間:2026-02-23 15:21:29