集成電路版圖設計與Cadence工具應用

隨著半導體技術的飛速發展,集成電路設計已成為電子工程領域的核心。其中,版圖設計作為集成電路物理實現的關鍵環節,直接決定了芯片的性能、功耗和可靠性。本文將從集成電路版圖設計的基本概念出發,探討Cadence工具在版圖設計中的應用,并分析其在實際項目中的重要性。

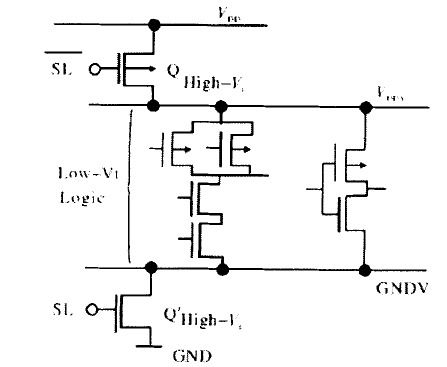

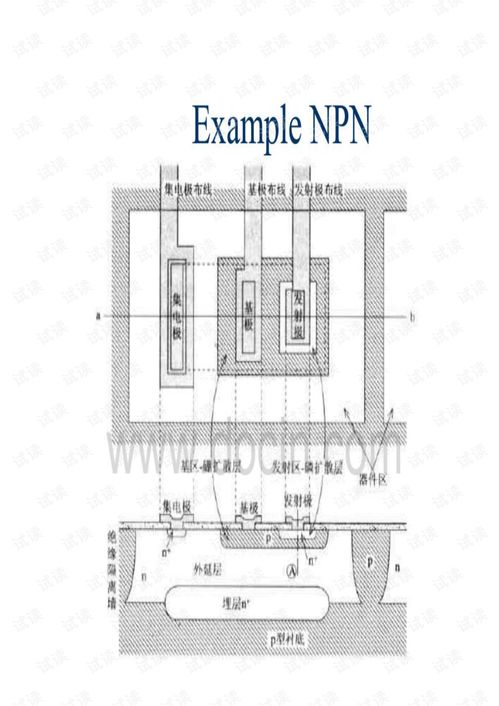

集成電路版圖設計是將電路邏輯轉換為物理布局的過程。設計者需要根據電路原理圖,在硅片上布置晶體管、電阻、電容等元件,并通過金屬互連層實現電氣連接。這一過程不僅需要考慮電路功能的正確性,還必須兼顧制造工藝的限制,如最小線寬、間距規則等。優秀的版圖設計能夠顯著提升芯片的良率和性能,同時降低生產成本。

在版圖設計工具中,Cadence Virtuoso是業界廣泛使用的平臺。它提供了從原理圖輸入、版圖編輯到驗證的全套解決方案。設計者可以通過Virtuoso的圖形界面直觀地進行版圖繪制,并利用其強大的設計規則檢查(DRC)和電路與版圖一致性檢查(LVS)功能,確保設計符合制造要求且與原始電路一致。Cadence工具還支持參數化單元(PCells)和自動化腳本,大大提高了設計效率。

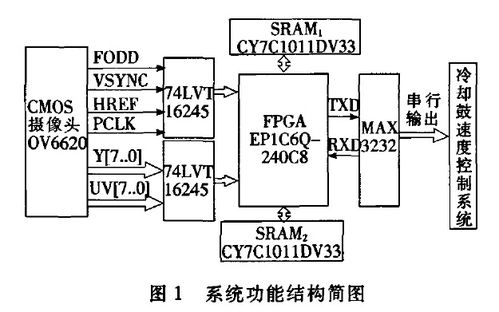

以eetop.cn網站提供的《集成電路版圖layout設計與cadence講義.pdf》為例,該資料系統地介紹了版圖設計的基礎知識和Cadence工具的操作方法。內容包括MOSFET的版圖結構、匹配與對稱性設計、電源與地線布局技巧,以及如何利用Cadence進行層次化設計和后仿真。這些內容對于初學者和進階設計者都具有重要參考價值。

在實際項目中,集成電路版圖設計往往需要跨學科協作。設計者必須與工藝工程師、電路設計師緊密配合,理解工藝參數對版圖的影響,并優化布局以應對信號完整性、功耗和散熱等挑戰。隨著工藝節點不斷縮小,版圖設計中的寄生效應和可制造性問題日益突出,這使得工具如Cadence的先進功能變得不可或缺。

集成電路版圖設計是連接電路設計與芯片制造的橋梁,而Cadence工具則為這一過程提供了強有力的支持。通過系統學習相關資料如eetop.cn的講義,并結合實際項目經驗,設計者能夠掌握高效的版圖設計方法,為開發高性能、低功耗的集成電路奠定堅實基礎。隨著人工智能和云計算技術的融入,版圖設計工具將進一步提升自動化水平,推動集成電路產業持續創新。

如若轉載,請注明出處:http://m.gzclyk.cn/product/36.html

更新時間:2026-02-23 22:56:26